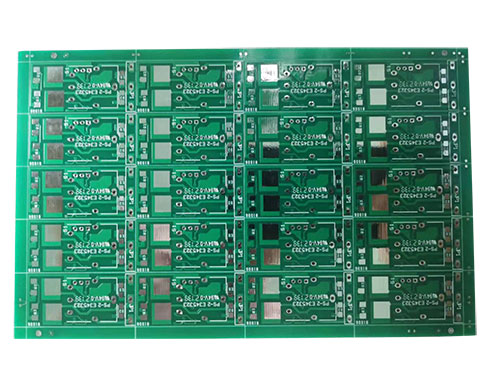

在pcb打樣設(shè)計電路圖時,需要考慮電路的功率和信號完整性。功率方面,需要確定每個元件的功率需求,以便選擇適當?shù)脑碗娫础P盘柾暾苑矫妫枰⒁庾杩蛊ヅ洹⑿盘杺鬏斁€路的長度和方向,以便最小化信號失真和反射。此外,還需要考慮EMC(電磁兼容性)問題,以確保電路板不會干擾或受到干擾。

除了這些因素,注意細節(jié)也是pcb打樣電路圖設(shè)計和布局中非常重要的一部分。例如,布線的長度需要盡量短,以減少信號的傳輸延遲和功率損耗。同時,需要合理地布置元件,盡量避免元件之間的互相干擾。阻抗匹配也非常關(guān)鍵,需要盡量避免出現(xiàn)阻抗不匹配的情況,以減少信號失真和反射。

在處理信號地時,需要將信號地和電源地分離開來,并使用恰當?shù)倪B接方式,以減少地線回流和干擾。此外,在電路板的布局過程中,還需要避免出現(xiàn)晶體管、電感和電容等元件之間的相互影響,以減少噪聲和干擾。

在設(shè)計和布局電路圖時,需要使用專業(yè)的軟件,如Altium Designer、Eagle PCB等,以便更好地完成這一任務(wù)。這些軟件提供了各種工具和資源,可以幫助工程師更好地完成電路圖的設(shè)計和布局。此外,還需要使用模擬器和仿真器,以驗證電路的性能和穩(wěn)定性,確保電子產(chǎn)品的質(zhì)量和可靠性。

綜上所述,電路圖的設(shè)計和布局是PCB打樣過程中最重要和最具挑戰(zhàn)性的工序之一。在進行電路圖的設(shè)計和布局時,需要考慮各種因素,如功率、信號完整性、EMC等等,以確保電子產(chǎn)品的質(zhì)量和可靠性。注意細節(jié)也非常重要,以減少信號失真、反射和噪聲干擾等問題。

*本站所有相關(guān)知識僅供大家參考、學習之用,部分來源于互聯(lián)網(wǎng),其版權(quán)均歸原作者及網(wǎng)站所有,如無意侵犯您的權(quán)利,請與小編聯(lián)系,我們將會在第一時間核實,如情況屬實會在3個工作日內(nèi)刪除;如您有優(yōu)秀作品,也歡迎聯(lián)系小編在我們網(wǎng)站投稿! 7*24小時免費熱線: 135-3081-9739

文章關(guān)鍵詞:PCB打樣哪個步驟工序最難,PCB,PCB廠家下一篇: 淺析PCB線路板增層法制作工藝

掃碼快速獲取報價

135-3081-9739