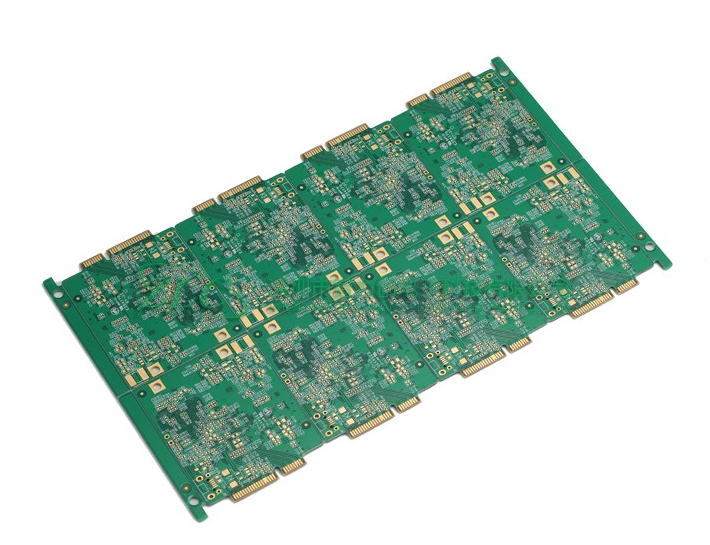

PCB線路板打樣制造的抗干擾設(shè)計(jì)與線路布局有著密不可分的關(guān)系,如何設(shè)計(jì)和能有效減少電路抗干憂的困擾,下面就PCB抗干憂設(shè)計(jì)問題做一個簡單的講解!

1、電源線設(shè)計(jì):根據(jù)打樣線路板電流的大小,在設(shè)計(jì)電源線時盡量加粗電源寬度,適當(dāng)減少環(huán)路電阻,使電源線、地線走向與數(shù)據(jù)傳遞方向一致,這樣設(shè)計(jì)有助于加強(qiáng)抗噪聲能力。

2、地線設(shè)計(jì):數(shù)字地與模擬地應(yīng)在分開設(shè)計(jì),假如電路板上既有邏輯電路又有線性電路,設(shè)計(jì)時應(yīng)盡量將其分開。即使是低頻電路也應(yīng)盡量采用單點(diǎn)并聯(lián)接地,實(shí)際布線有困難時可部分串聯(lián)后再并聯(lián)接地。高頻電路板宜采用多點(diǎn)串聯(lián)接地,地線應(yīng)短而租,高頻元件周圍盡量用柵格狀大面積地箔。盡量加粗接地線設(shè)計(jì),如接地線用很紉的線條,則接地電位隨電流的變化而變化,使其抗噪性能降低。若設(shè)計(jì)時加粗接地焉,可使它能通過三倍于印制板上的允許電流。再者設(shè)計(jì)接地線時盡量使其構(gòu)成閉環(huán)路,由數(shù)字電路組成的層,其接地電路布成團(tuán)環(huán)路能一定程度上加強(qiáng)抗噪聲能力。

3、退藕電容配置:標(biāo)準(zhǔn)電源輸入端跨接10~100uf的電解電容器,每個集成電路芯片都應(yīng)布置一個0.01pF的瓷片電容,遇到印制板空隙不夠時,可在每4~8個芯片布置一個1~10pF的但電容,對于抗噪能力弱、關(guān)斷時電源變動較大的器件,應(yīng)在芯片的的電源線和地線之間直接接入退藕電容,最后切記電容引線不易過長,特別是高頻旁電路電路不能出現(xiàn)引線。

*本站所有相關(guān)知識僅供大家參考、學(xué)習(xí)之用,部分來源于互聯(lián)網(wǎng),其版權(quán)均歸原作者及網(wǎng)站所有,如無意侵犯您的權(quán)利,請與小編聯(lián)系,我們將會在第一時間核實(shí),如情況屬實(shí)會在3個工作日內(nèi)刪除;如您有優(yōu)秀作品,也歡迎聯(lián)系小編在我們網(wǎng)站投稿! 7*24小時免費(fèi)熱線: 135-3081-9739

文章關(guān)鍵詞:PCB線路板打樣,PCB線路板制造,PCB電路板抗干擾掃碼快速獲取報(bào)價

135-3081-9739